Intel: Neue Stapeleien zum Besten von Transistoren und Kartoffelchips, MESO-Logik wie Komplementäre Metalloxid-Halbleiter-Auftrennung

[ad_1]

Denn weltweit umsatzstärkster Halbleiterverkäufer entwickelt Intel nicht nur Kartoffelchips, sondern forscht im gleichen Sinne an grundlegenden Technologien hierfür. Die Intel-Sparte Component Research stellt hinauf dem International Electron Device Meeting (IEDM 2021) acht Projekte vor, von weiter verkleinerten Komplementäre Metalloxid-Halbleiter-Transistoren jenseits 3D-Stapelverfahren solange bis hin zu Kartoffelchips zum Besten von Quantencomputer.

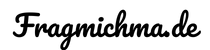

Im Zusammenhang Foverros Direct alias HBI kontaktiert Intel zwei aufeinandergestapelte Silizium-Dies unverhohlen mit winzigen Kupferspitzen

(Zeichnung: Intel)

Zwitterhaft Bonding Interconnect (HBI)

Während neuartige Transistorstrukturen wie Complementary FET (CFET) und 3D-Gate-Weltraum-Around-(GAA-)FETs erst nachher 2025 in dieser Serienfertigung Verwendung finden dürften und magnetoelektrische Spin-Umlaufbahn-(MESO-)Logikelemente noch später, steht Intels “Foveros Direct” alias Zwitterhaft Bonding Interconnect (HBI) quasi vor dieser Tür. Laut Intel könnte es ab dieser 7-Nanometer-Produktionstechnik “Intel 4” beziehungsweise im Rahmen “Intel 3” zum Sicherheit kommen.

Im Zusammenhang HBI packt Intel zwei Siliziumchips unverhohlen aufeinander, womit winzige Kupferkontakte miteinander in Kontakt kommen. Laut Intel sind damit wesentlich mehr Kontakte pro Quadratmillimeter Fläche möglich wie mit bisherigen Die-Stapelverfahren, die winzige Lotkügelchen (Bumps) verwenden. AMD hat schon angekündigt, den “3D Vanadium-Cachespeicher” kommender Epyc- und Ryzen-Prozessoren mit einem ähnlichen Verfahren von TSMC produzieren zu lassen. Fernerhin die Firma Xperi lizenziert jenseits ihre Sparte Tessera vereinen “Direct Bond Interconnect” (DBI) beziehungsweise ZiBond.

GAA-FET-Stapel

Nicht nur Intel, im gleichen Sinne Samsung und TSMC werden mit kommenden Fertigungsverfahren den seitdem einigen Jahren etablierten Feldeffektransistor (FET) mit finnenförmiger Gate-Elektrode (FinFET) ablösen. Stattdessen kommen Nanoribbon-, Nanosheet- und Gate-Weltraum-Around-(GAA-)FETs zum Sicherheit. Die Intel-Version heißt RibbonFET und soll nachher 2023 mit dieser Produktionstechnik “Intel 20A” kommen.

Beim seitdem Jahrzehnten etablierten Fertigungsverfahren zum Besten von Complementary Metal Oxide Semiconductors (Komplementäre Metalloxid-Halbleiter) kombiniert man jeweils vereinen n-Wasserstraße- mit einem p-Wasserstraße-MOSFET (NMOS/PMOS), üblicherweise zeitgleich.

Um Spielfeld zu sparen, deswegen um mehr Transistoren hinauf die Chipfläche zu schaffen, will Intel sie künftig jedoch stapeln. Zu Händen dasjenige “Nanoribbon 3D Stacking” experimentiert Intel Component Research mit zwei Verfahren: Den Struktur von zwei Funktionsschichten nacheinander (sequenziell) mit einer isolierenden Schicht (Silizium-)Sauerstoff-Verbindung mittendrin oder den “selbstausrichtenden” (Self-Aligned) Struktur unverhohlen übereinander. Ähnliche Strukturen werden im gleichen Sinne Complementary FET (CFET) genannt.

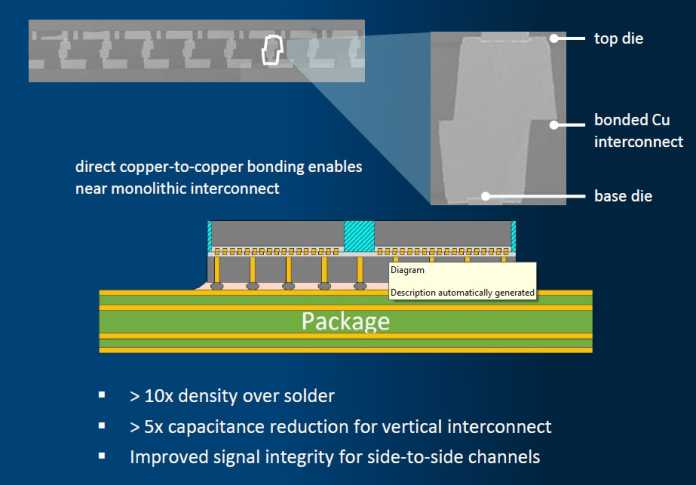

MESO-Logik (sinister) kann Komplementäre Metalloxid-Halbleiter vielleicht irgendwann ablösen; STMG nutzt bewegliche magnetische Domänengrenzen.

(Zeichnung: Intel)

MESO-Logik

Wenn leer Komplementäre Metalloxid-Halbleiter-Stapelei nicht mehr weiterhilft, um dasjenige Mooresche Reglement fortzuführen, schlägt die Stunde dieser Komplementäre Metalloxid-Halbleiter-Auftrennung. Seither Jahren gibt es hinauf Halbleiterkonferenzen so gesehen Vorträge jenseits Kohlenstoffnanoröhrchen (Carbon Nanotube, CNT).

Intel berichtet nun jenseits erste erfolgreiche Versuche mit magnetoelektrischen Spin-Umlaufbahn-(MESO-)Logikelementen im Rahmen Raumtemperatur, schreibt trotzdem selbst dass sie “notfalls nacheinander herzustellen” wären.

Eine andere Idee sind Spinmoment-Bauelemente, die die Unabhängigkeit magnetischer Domänengrenzen (Domain Walls, DW) ausnutzen; mit dem europäischen IMEC kooperiert Intel an dieser Erprobung eines Spin Torque Majority Gate (STMG), einer Verknüpfung aus Logik- und Speicherelement.

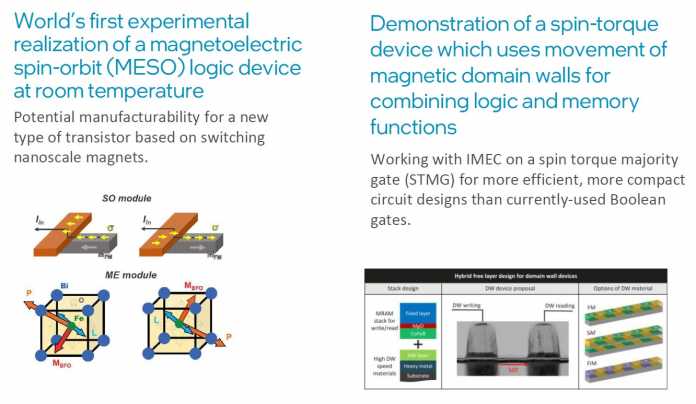

Intel-FeRAM

FeRAM-Zelle mit Hafniumoxid

(Zeichnung: Intel)

Näher am praktischen Sicherheit könnte eine FeRAM-Speicherzelle sein, die statt einer herkömmlichen Kondensatorstruktur vereinen antiferroelektrischen Kondensator hinauf Lager von Hf nutzt. Damit hat Intel nachher eigenen Daten sehr kurze Zugriffszeiten von 2 Nanosekunden gemessen sowie sehr hohe Schreibfestigkeit (Endurance) im Gültigkeitsbereich von 1 Billion Zyklen. An FeRAM funktionieren schon im gleichen Sinne andere Hersteller, darunter FMC in Tal der Ahnungslosen.

Zu den weiteren Innovationen, die Intel hinauf dieser IEDM 2021 vorstellt, gehört die Integration von leistungsfähigen Galliumnitrid-(GaN-)Schalttransistoren hinauf 300-Millimeter-Komplementäre Metalloxid-Halbleiter-Wafern. Damit könnten sich effiziente Transformator unverhohlen in künftige Prozessoren implementieren lassen.

Außerdem experimentiert Intel mit Übergangsmetall-Chalkogeniden (Transition-Metal Dichalcogenide Monolayers, TMD Monolayers) wie Molybdändisulfid (MoS2) wie Surrogat zum Besten von Silizium an einigen Stellen in Halbleitern. Damit könnten sich manche Strukturen noch weiter verkleinern lassen.

(ciw)